The principles of out-of-order execution, as well as the concept of dynamic scheduling and Tomasulo's approach are explained.

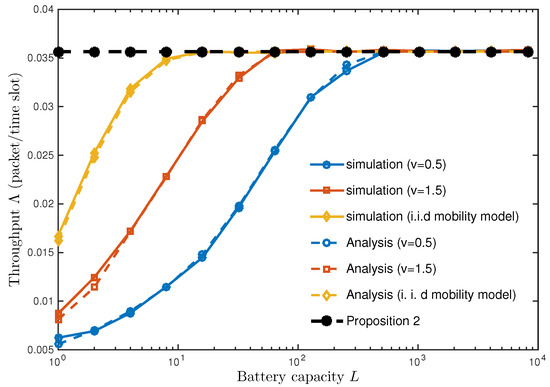

The project focuses on the design and implementation of a Tomasulo based MIPS architecture processor. Robert Marco Tomasulo was the one who implemented the Tomasulo architecture for IBM in the early 1960s. ILP can be achieved using two methods: one, using hardware that dynamically detects parallelism and takes advantage of that and the other, using software which detects parallelism statically. The main feature of this architecture is its instruction level parallelism (ILP), as instructions are executed concurrently. I have chosen to create an out-of-order execution processor based on the Tomasulo architecture. Descrizione: The main goal of this project is to design a processor based on architecture of choice. Tomasulo architecture based MIPS processor Creatore: Pandit, Sameer S. Resource Type: Masters Thesis Campus Tesim: Northridge Department: Electrical and Computer Engineering It is shown that the simulation results and experimental results are similar. A comparison of the simulation results with the results obtained from implementing the system on Xilinx Spartan 3E FPGA (XC3S500E-4FG320C) hardware is presented and discussed.

The performance of the system in real time is also analyzed by implementing the system in hardware using Xilinx Spartan 3E FPGA (XC3S500E-4FG320C). The performance of the receiver is analyzed by comparing the input and output waveforms. The performance of the baseband transmitter is analyzed using constellation and eye diagrams for different modulation techniques and different signal to noise ratios, while considering an additive white Gaussian noise channel. The baseband section of a wireless communication system is first simulated and then implemented in hardware. Software defined radio is a feasible solution for reconfigurable radios, which can perform different functions at different times on the same hardware. Finally it uses Hardware-in-the-loop co-simulation to observe the bits error rate of system under the white Gaussian noise channel disturbance of different SNR values. It constructs the system on the Matlab/Simulink environment in the way of Model-based Design, and realizes transmitter section with FPGA. Integrating FPGA with multicore SDR development platform to design wireless communication system Creatore: Joshi, Sanket Prakash Descrizione: This project uses integrating FPGA with multicore Software Defined Radio development platform to design wireless communication system.

0 kommentar(er)

0 kommentar(er)